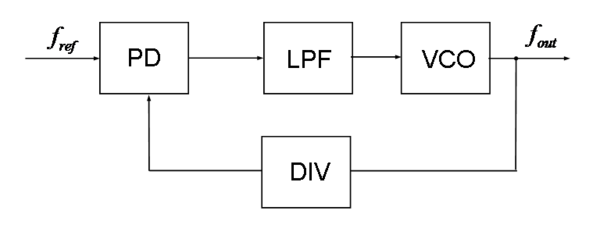

锁相回路(PLL: Phase-locked loops)是一种利用反馈(Feedback)控制原理实现的频率及相位的同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。当参考时钟的频率或相位发生改变时,锁相回路会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者重新同步,这种同步又称为“锁相”(Phase-locked)。

锁相回路在众多领域有应用,如无线通信、数字电视、广播等。具体的应用范围包括但不限于:

一个锁相回路电路通常由以下模块构成:

每个模块的简单原理描述如下:

对于锁相回路来说,最关键的性能是在于相位噪声(英语:Phase noise)和动态性能。

另外,锁相回路的稳定性指标包括:环路带宽(Loop bandwidth),相位裕度(Phase margin)等。